SRAM And ROM Design IP Market Size and Trends

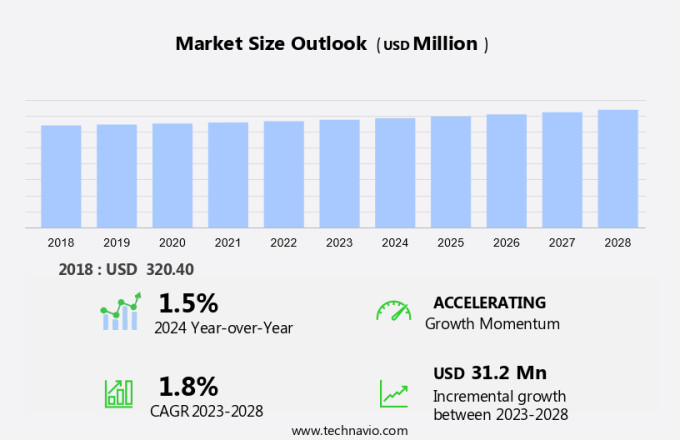

The SRAM And ROM Design IP market size is forecast to increase by USD 31.2 million, at a CAGR of 1.8% between 2023 and 2028. The market is experiencing significant growth due to the increasing demand for power-efficient solutions in various applications. One of the primary drivers is the expanding data center sector, where low-power SRAM and ROM designs are essential for data processing and power consumption management. Additionally, the proliferation of connected devices, 5G networks, and edge computing are fueling the need for high-density, low-power memory solutions. Autonomous vehicles and non-volatile memory technologies are also contributing to market growth. In the automotive industry, SRAM and ROM IP are crucial for data processing and storage in advanced driver assistance systems (ADAS) and autonomous driving applications. Furthermore, the adoption of non-volatile memory, such as MRAM and ReRAM, is increasing due to their ability to offer higher density, lower power consumption, and faster access times compared to traditional volatile memory. Enterprise storage and cloud storage are other significant markets for SRAM and ROM Design IP. Hyper-converged infrastructure(HCI) and other data processing applications require high-performance, low-power memory solutions to handle increasing data workloads efficiently. The market analysis report also highlights the challenges faced by the market, including scaling issues and the need for further innovation to meet the evolving demands of various applications.

The SRAM (Static Random Access Memory) and ROM (Read-Only Memory) Design IP market represents a significant segment in the semiconductor industry, catering to the increasing demand for memory solutions in data-intensive applications. These applications span across various domains, including artificial intelligence (AI), machine learning, big data analytics, Internet of Things (IoT), and other electronics components. Memory-intensive applications, such as microcontrollers, embedded systems, programmable devices, and application-specific integrated circuits (ASICs), require high-performance, compact memory technologies. SRAM and ROM design IPs offer solutions that meet these demands, ensuring optimal memory density and power consumption. SRAM technologies have gained popularity due to their fast read and write access times, making them suitable for applications requiring frequent data access. On the other hand, ROM technologies offer the benefits of non-volatility, ensuring data retention even without power. The SRAM market continues to evolve, with a focus on low power consumption and compact technologies.

Small SRAM modules, such as Serial Peripheral Interface (SPI) SRAMs and Synchronous On-Chip Memory (SOM), cater to the needs of low-power computer vision applications and other power-sensitive systems. Design intellectual property (IP) plays a crucial role in the semiconductor manufacturing process. SRAM and ROM design IPs enable OEM manufacturers to integrate these memory solutions into their products efficiently, reducing development time and costs. In the context of data centers, SRAM and ROM design IPs contribute to the development of high-performance, energy-efficient memory solutions. These solutions enable faster data processing, reducing latency and enhancing overall system performance. In conclusion, the market offers essential memory solutions for memory-intensive applications across various domains. The focus on compact technologies, low power consumption, and high memory density ensures that these solutions cater to the evolving needs of the semiconductor industry. By integrating SRAM and ROM design IPs into their products, OEM manufacturers can deliver innovative, high-performance solutions to their customers.

Market Segmentation

The market research report provides comprehensive data (region-wise segment analysis), with forecasts and estimates in "USD million" for the period 2024-2028, as well as historical data from 2018 - 2022 for the following segments.

- Type

- SRAM

- ROM

- Geography

- APAC

- China

- India

- Japan

- South Korea

- North America

- Canada

- US

- Europe

- Germany

- France

- Italy

- Spain

- South America

- Middle East and Africa

- APAC

By Type Insights

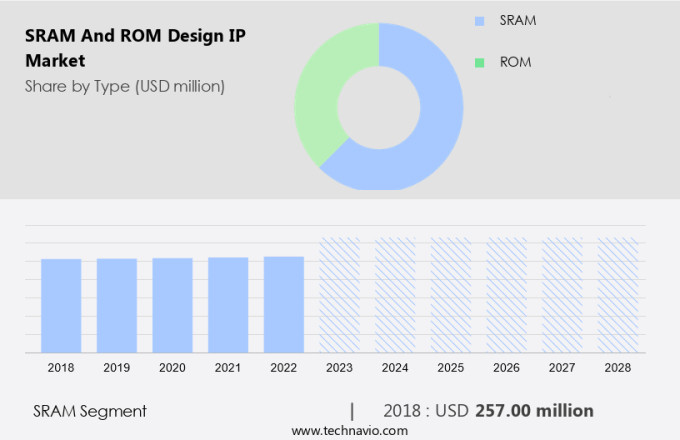

The SRAM segment is estimated to witness significant growth during the forecast period. The market encompasses solutions that cater to power consumption requirements in various sectors, including data centers, connected devices, and autonomous vehicles. Power efficiency is crucial in data processing for data centers, where 5G and edge computing are driving the need for low-power solutions. In the realm of connected devices, the demand for high-density memory and non-volatile memory is escalating. These memory types ensure data retention even when power is disconnected. Enterprise and cloud storage are other significant areas where SRAM and ROM Design IP play a pivotal role. Hyper-converged infrastructure (HCI) is a popular solution in these domains, offering efficient data processing and storage.

Get a glance at the market share of various segments Download the PDF Sample

The SRAM segment was valued at USD 257.00 million in 2018. The integration of SRAM and ROM Design IP in HCI enables faster access to data and improved overall system performance. In the context of the US market, the demand for SRAM and ROM Design IP is growing as businesses seek to optimize power consumption and enhance data processing capabilities. As data-intensive applications become more prevalent, the need for reliable and efficient memory solutions is increasing. By implementing SRAM and ROM Design IP, organizations can ensure their systems maintain high performance while minimizing power consumption. In summary, the market offers essential solutions for power management and data processing in various industries, including data centers, connected devices, and enterprise storage. These solutions enable faster access to data, improved system performance, and power efficiency, making them indispensable in today's technology landscape.

Regional Analysis

For more insights on the market share of various regions Download PDF Sample now!

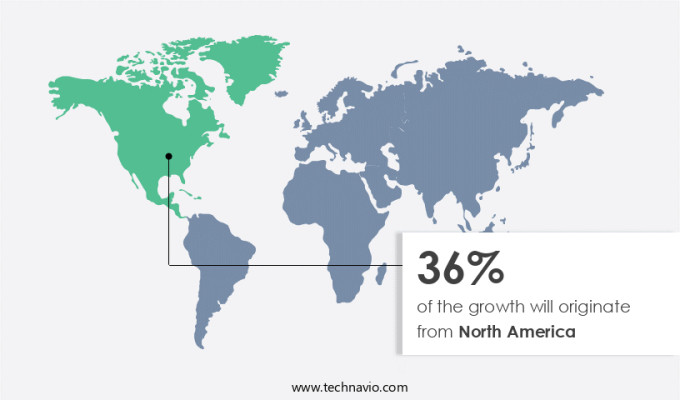

North America is estimated to contribute 36% to the growth of the global market during the forecast period. Technavio's analysts have elaborately explained the regional trends and drivers that shape the market during the forecast period. The enterprise storage market in North America is experiencing significant growth due to increasing demand for cache memory in microprocessors and firmware for boot codes. In addition, the rise of cloud storage solutions and wireless networks necessitates high-density and low-power storage solutions. Memory architectures, such as Dynamic Random Access Memory (DRAM), are essential for online content delivery and data processing in various industries. China and Taiwan are major players in the global semiconductor industry, with China's JCET Group Co., Ltd., and Taiwan's Taiwan Semiconductor Manufacturing Company (TSMC) accounting for a significant portion of the sales of SRAM and ROM. These companies' contributions are crucial to the semiconductor industry's growth.

The demand for SRAM and ROM designs in the IP market is increasing due to the need for efficient memory solutions for various applications. The semiconductor industry's growth is also influenced by the industrial demand for memory solutions and the increasing popularity of wireless networks and online content. As a result, memory producers are focusing on developing advanced memory architectures and technologies to meet the growing demand for high-density and low-power storage solutions. In summary, the North American market for SRAM and ROM designs in the IP market is expected to grow substantially due to the increasing demand for efficient memory solutions in various industries. China and Taiwan's significant contributions to the global semiconductor industry further highlight the importance of these memory solutions.

Our researchers analyzed the data with 2023 as the base year, along with the key drivers, trends, and challenges. A holistic analysis of drivers will help companies refine their marketing strategies to gain a competitive advantage.

SRAM And ROM Design IP Market Driver

Faster processing speed is notably driving market growth. Electronic components, such as microcontrollers and programmable devices, play a crucial role in consumer electronics and embedded systems. These components include applicationspecific ICs (ASICs) and SRAM technologies. SRAM, or Static Random Access Memory, is a type of electronics memory that does not require refreshing like DRAM (Dynamic Random Access Memory). This results in faster access times, with SRAM accomplishing tasks within 10 nanoseconds, compared to DRAM's 60 nanoseconds.

SRAM is preferred in applications where low power consumption and compact technologies are essential, such as SoM (System on Module), lowpower computer vision, and on-device machine learning. OEM manufacturers benefit from the use of SRAM due to its small SRAM modules and fast processing capabilities. In the realm of electronics, SRAM's advantages make it an indispensable component for various applications. Thus, such factors are driving the growth of the market during the forecast period.

SRAM And ROM Design IP Market Trends

Increasing demand for enterprise storage applications to drive growth for MRAM is the key trend in the market. Magneto resistive random-access memory (MRAM) is a non-volatile memory technology that utilizes magnetic domains to store data. MRAM offers similar write endurance and data retention to Dynamic Random-Access Memory (DRAM), yet boasts lower latency access and bit error rates, making it an ideal choice for caching critical data in enterprise storage systems. The enterprise storage sector is experiencing substantial growth due to the increasing demand for IoT, AI, and big data applications.

The advent of advanced wireless networks, such as 5G, is anticipated to further fuel this growth in data centers and edge computing. MRAM's high performance and suitability for such memory-intensive applications make it a desirable solution for these expanding markets. The semiconductor manufacturing industry continues to innovate, increasing memory density to meet the demands of these applications. MRAM's potential to enhance system performance and reliability makes it a valuable asset in the data storage landscape. Thus, such trends will shape the growth of the market during the forecast period.

SRAM And ROM Design IP Market Challenge

The scaling issue of SRAM is the major challenge that affects the growth of the market. SRAM and ROM memory technologies, including qSPI flash and qSPI SRAM, continue to be essential components in various applications, such as IoT and wireless devices, medical equipment, and utilities. However, scaling challenges persist in SRAM, primarily due to issues with cell stability and physical area. The minimum operating voltage (VMIN) of an SRAM is influenced by transistor voltage (Vt) mismatch, which is comprised of structural and random dopant fluctuation (RDF). The inverse relationship between Vt mismatch and device/cell size implies that larger cells exhibit greater stability. To mitigate scaling challenges in SRAM, chipmakers must weigh the advantages of planar transistors against finFETs in their manufacturing processes. This involves balancing various trade-offs to ensure optimal performance and reliability.

In the realm of flash memory, advancements include the integration of EEProduct innovations in this sector continue to drive growth, with applications in IoT, wireless, medical, and utility sectors. Scaling challenges in SRAM, specifically related to cell stability and physical area, necessitate careful process and design choices for chipmakers. The inverse relationship between transistor voltage mismatch (Vt) and device/cell size implies that larger cells exhibit greater stability. To address these challenges, manufacturers must consider the advantages of planar transistors versus finFETs in their manufacturing processes, striking a balance between performance, reliability, and cost-effectiveness. Hence, the above factors will impede the growth of the market during the forecast period.

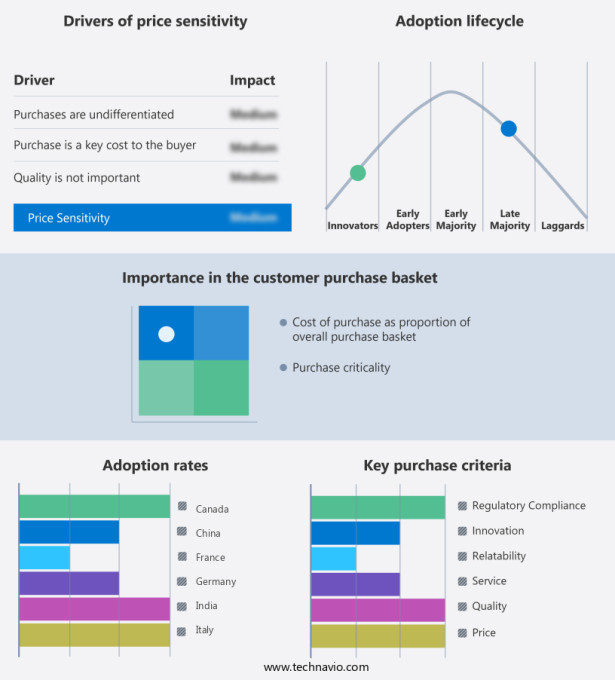

Exclusive Customer Landscape

The market forecasting report includes the adoption lifecycle of the market, covering from the innovator's stage to the laggard's stage. It focuses on adoption rates in different regions based on penetration. Furthermore, the report also includes key purchase criteria and drivers of price sensitivity to help companies evaluate and develop their market growth analysis strategies.

Customer Landscape

Key Companies & Market Insights

Companies are implementing various strategies, such as strategic alliances, partnerships, mergers and acquisitions, geographical expansion, and product/service launches, to enhance their presence in the market.

ADVANCED MICRO DEVICES INC. - The company offers SRAM and ROM design IP products such as Block Memory Generator LogiCORE IP core.

The market research and growth report also includes detailed analyses of the competitive landscape of the market and information about key companies, including:

- AnySilicon

- Arm Ltd.

- Avalanche Technology Inc.

- Cadence Design Systems Inc.

- CEVA Inc.

- Dolphin Technology Inc

- eMemory Technology Inc.

- Everspin Technologies Inc.

- Infineon Technologies AG

- Integrated Silicon Solution Inc.

- Microchip Technology Inc.

- Renesas Electronics Corp.

- STMicroelectronics International NV

- Surecore Ltd

- Synopsys Inc.

- Toshiba Corp.

Qualitative and quantitative analysis of companies has been conducted to help clients understand the wider business environment as well as the strengths and weaknesses of key market players. Data is qualitatively analyzed to categorize companies as pure play, category-focused, industry-focused, and diversified; it is quantitatively analyzed to categorize companies as dominant, leading, strong, tentative, and weak.

The market, specifically for SRAM and ROM designs, is experiencing significant growth due to the increasing demand for memory-intensive applications in various sectors. Artificial intelligence (AI) and machine learning (ML) are driving this trend, as these technologies require large amounts of data storage for training and inference. Big data analytics, IoT, and 5G are also contributing to the growth, as they generate vast amounts of data that need to be processed and stored efficiently. Semiconductor manufacturing companies are scaling up their memory production to meet the increasing demand for high-density memory with low power consumption. Memory density and power consumption are critical factors in the design of SRAM and ROM IP for data centers, connected devices, and edge computing. Advanced technology architectures are being developed to address scaling obstacles such as transistor Vt mismatch and cell stability. Static Random Access Memory (SRAM) and Read-Only Memory (ROM) are essential components in the design of microprocessors, firmware, boot code, and cache memory.

SRAM and ROM IP are used in various applications, including cloud storage solutions, low-power storage, and high-density storage. Memory architectures such as DRAM, QSPI flash, QSPI SRAM, and ROM memory technology are being innovated to meet the demands of wireless networks, online content, and storage producers. The market is expanding in the electronics components sector, with applications in consumer electronics, microcontrollers, embedded systems, programmable devices, and application-specific ICs. Compact technologies and small SRAM modules are being developed for low-power computer vision and on-device machine learning. Eeprom and flash memory are also essential components in the design of SRAM and ROM IP. Product innovations in these areas are driving growth in the IoT, wireless, medical, utility, and other applications.

|

Market Scope |

|

|

Report Coverage |

Details |

|

Page number |

161 |

|

Base year |

2023 |

|

Historic period |

2018 - 2022 |

|

Forecast period |

2024-2028 |

|

Growth momentum & CAGR |

Accelerate at a CAGR of 1.8% |

|

Market Growth 2024-2028 |

USD 31.2 million |

|

Market structure |

Fragmented |

|

YoY growth 2023-2024(%) |

1.5 |

|

Regional analysis |

APAC, North America, Europe, South America, and Middle East and Africa |

|

Performing market contribution |

North America at 36% |

|

Key countries |

US, Germany, China, France, Italy, Canada, South Korea, Japan, Spain, and India |

|

Competitive landscape |

Leading Companies, Market Positioning of Companies, Competitive Strategies, and Industry Risks |

|

Key companies profiled |

ADVANCED MICRO DEVICES INC., AnySilicon, Arm Ltd., Avalanche Technology Inc., Cadence Design Systems Inc., CEVA Inc., Dolphin Technology Inc, eMemory Technology Inc., Everspin Technologies Inc., Infineon Technologies AG, Integrated Silicon Solution Inc., Microchip Technology Inc., Renesas Electronics Corp., STMicroelectronics International NV, Surecore Ltd, Synopsys Inc., and Toshiba Corp. |

|

Market dynamics |

Parent market analysis, Market growth inducers and obstacles, Fast-growing and slow-growing segment analysis, COVID-19 impact and recovery analysis and future consumer dynamics, Market condition analysis for market forecast period. |

|

Customization purview |

If our market report has not included the data that you are looking for, you can reach out to our analysts and get segments customized. |

What are the Key Data Covered in this Market Research Report?

- CAGR of the market during the forecast period

- Detailed information on factors that will drive the market growth and forecasting between 2024 and 2028

- Precise estimation of the size of the market and its contribution of the market in focus to the parent market

- Accurate predictions about upcoming market growth and trends and changes in consumer behaviour

- Growth of the market across APAC, North America, Europe, South America, and Middle East and Africa

- Thorough analysis of the market's competitive landscape and detailed information about companies

- Comprehensive analysis of factors that will challenge the growth of market companies

We can help! Our analysts can customize this market research report to meet your requirements.